Courtesy of Forbes

Cadence Tembus Batas Baru Chiplet untuk Masa Depan Semikonduktor Modular

Menginformasikan kemajuan Cadence Design Systems dalam mengembangkan system chiplet yang berhasil diuji pada silicon nyata, guna mempercepat adopsi arsitektur chiplet modular yang lebih efisien dan fleksibel dalam industri semikonduktor, khususnya untuk aplikasi edge dan AI fisik.

14 Nov 2025, 03.29 WIB

150 dibaca

Share

Ikhtisar 15 Detik

- Cadence Design Systems telah berhasil membawa arsitektur chiplet ke dalam silicon, membuka peluang untuk desain sistem yang lebih modular.

- Chiplet memungkinkan desain yang fleksibel dengan menggabungkan berbagai fungsi dan node proses secara lebih efisien.

- Validasi UCIe dan LPDDR5X menunjukkan bahwa Cadence berada di jalur untuk memimpin dalam interoperabilitas dan kinerja chiplet di industri semikonduktor.

Industri semikonduktor menghadapi tantangan besar akibat semakin sulitnya memproduksi chip monolitik besar dan mahal. Cadence Design Systems menawarkan solusi dengan system chiplet, yaitu sebuah chip yang mengelola berbagai chiplet dalam satu SoC modular.

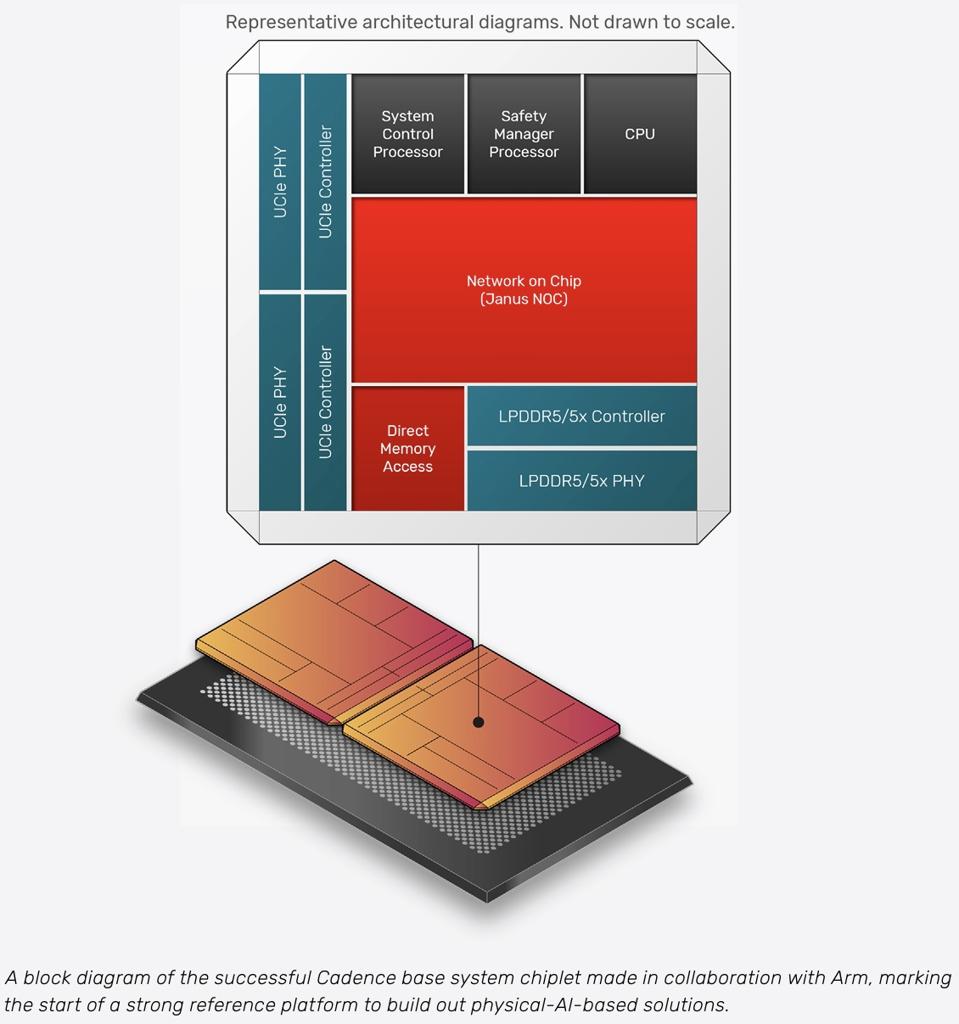

System chiplet Cadence menggabungkan berbagai komponen penting seperti prosesor, pengontrol, Network on Chip, dan PHY IP memori LPDDR5, semua terhubung lewat standar UCIe yang baru dan cepat. Keberhasilan mereka diuji nyata dalam silicon, bukan hanya simulasi.

Mereka berhasil memulai memori LPDDR5X pada kecepatan tinggi 9,600 MT/s antar chiplet, bahkan mencapai kecepatan lebih tinggi dalam kondisi tertentu. Hal ini membuktikan bahwa standar dan teknologi mereka sangat siap untuk aplikasi praktis.

Desain chiplet modular memudahkan pengembang mencampur berbagai node proses dan fungsi, yang bisa mempercepat waktu pemasaran, mengurangi risiko, dan meningkatkan hasil produksi. Cadence juga menyediakan acuan sistem chiplet yang bisa membantu developer mengurangi biaya dan mempercepat desain.

Ke depan, teknologi ini sangat relevan untuk pasar AI fisik dan edge yang butuh performa dan efisiensi tinggi. Meskipun ada tantangan dalam biaya paket dan manajemen termal, Cadence memimpin tren inovasi ini yang bisa jadi titik balik penting di industri semikonduktor.

Referensi:

[1] https://www.forbes.com/sites/marcochiappetta/2025/11/13/cadence-debuts-its-first-system-chiplet-silicon-to-accelerate-physical-ai-development/

[1] https://www.forbes.com/sites/marcochiappetta/2025/11/13/cadence-debuts-its-first-system-chiplet-silicon-to-accelerate-physical-ai-development/

Analisis Ahli

Jim Hogan (Teknologi Semikonduktor)

"Keberhasilan Cadence menunjukkan kematangan teknologi chiplet dan pentingnya standar interoperabilitas seperti UCIe yang bisa menjadi game changer dalam desain chip masa depan."

Lisa Su (CEO AMD)

"Pendekatan modular chiplet adalah arah yang tidak terelakkan bagi industri dan integrasi yang ditunjukkan Cadence dapat mempercepat adopsi solusi chiplet secara komersial."

Analisis Kami

"Cadence mengambil langkah strategis yang sangat tepat dengan menyediakan platform chiplet yang sudah terbukti di silicon nyata, mengatasi salah satu hambatan utama dalam desain multi-die yang selama ini banyak mengandalkan simulasi. Namun, tantangan biaya dan kompleksitas packaging masih harus diatasi agar inovasi ini benar-benar meluas dan dapat diimplementasikan secara massal di pasar dunia nyata."

Prediksi Kami

Dalam waktu dekat, platform chiplet Cadence akan semakin banyak diadopsi untuk pengembangan sistem embedded dan edge-AI, membuka peluang kolaborasi multi-vendor dan mempercepat inovasi di industri semikonduktor modular.

Pertanyaan Terkait

Q

Apa itu chiplet yang dikembangkan oleh Cadence Design Systems?A

Chiplet yang dikembangkan oleh Cadence adalah perangkat tunggal yang mencakup semua fungsi untuk mengelola sumber daya dari sistem SoC multi-chiplet.Q

Mengapa arsitektur chiplet penting dalam industri semikonduktor?A

Arsitektur chiplet penting karena memungkinkan desain yang lebih fleksibel dengan menggabungkan berbagai fitur dan node proses, mengatasi tantangan yang ditimbulkan oleh batasan ukuran monolitik SoC.Q

Apa yang dicapai oleh Cadence dengan memvalidasi memori LPDDR5X?A

Cadence berhasil menginisialisasi memori LPDDR5X pada kecepatan 9.600 MT/s, yang menunjukkan kemampuan sistem chiplet mereka dalam menghadapi tantangan sinyal dan integritas waktu.Q

Apa fungsi UCIe dalam konteks chiplet?A

UCIe berfungsi sebagai standar konektivitas antar chip yang mendukung interoperabilitas antara chiplet dari berbagai vendor, yang sangat penting untuk ekosistem chiplet.Q

Bagaimana perkembangan ini dapat mempengaruhi desain sistem di masa depan?A

Perkembangan ini dapat mempercepat adopsi arsitektur modular untuk sistem yang membutuhkan sumber daya komputasi dan bandwidth tinggi, terutama di bidang AI dan kendaraan otonom.